Edition 1.0 2013-08

# TECHNICAL REPORT

## RAPPORT TECHNIQUE

Documentation on design automation subjects – The Bird's-eye View of Design Languages (BVDL)

Documentation sur les sujets concernant l'automatisation de la conception – Langages BVDL (Bird's-eye View of Design Languages)

INTERNATIONAL ELECTROTECHNICAL COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

PRICE CODE CODE PRIX

ICS 25.040

ISBN 978-2-8322-1028-4

Warning! Make sure that you obtained this publication from an authorized distributor. Attention! Veuillez vous assurer que vous avez obtenu cette publication via un distributeur agréé.

Registered trademark of the International Electrotechnical Commission Marque déposée de la Commission Electrotechnique Internationale

## CONTENTS

| FOF                                                                     | FOREWORD                                                                                     |              |                                                     |    |  |  |

|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------|----|--|--|

| ΙΝΤΙ                                                                    | RODUCT                                                                                       | ION          |                                                     | 5  |  |  |

| 1                                                                       | Scope                                                                                        |              |                                                     | 6  |  |  |

| 2                                                                       | Structur                                                                                     | e and conte  | ent of the Bird's-eye View of Design Languages      | 8  |  |  |

|                                                                         | 2.1                                                                                          | Structure    | of the Bird's-eye View of Design Languages          | 8  |  |  |

|                                                                         | 2.2                                                                                          | Chart of d   | esign processes                                     | 9  |  |  |

|                                                                         | 2.3                                                                                          | Table of "   | Electronic system design"                           | 10 |  |  |

|                                                                         | 2.4                                                                                          | Table of "S  | SoC design"                                         | 10 |  |  |

|                                                                         | 2.5                                                                                          | Table of "I  | Mixed-signal verification" and analog block design" | 11 |  |  |

|                                                                         | 2.6                                                                                          | Table of "(  | Characterization and IP preparation"                | 12 |  |  |

|                                                                         | 2.7                                                                                          |              |                                                     |    |  |  |

|                                                                         |                                                                                              | 2.7.1        | General                                             | 13 |  |  |

|                                                                         |                                                                                              | 2.7.2        |                                                     | 13 |  |  |

|                                                                         |                                                                                              | 2.7.3        |                                                     | 14 |  |  |

| 3                                                                       | Use cas                                                                                      | e of the Bir | d's-eye View of Design Languages                    | 14 |  |  |

|                                                                         | 3.1                                                                                          |              |                                                     |    |  |  |

|                                                                         | 3.2                                                                                          |              | •                                                   |    |  |  |

|                                                                         | 3.3                                                                                          | Case 3): E   | Emergence of new technology                         | 15 |  |  |

| 4                                                                       | The Birc                                                                                     | l's-eye Viev | w of Design Languages (BVDL), version 1.0           | 15 |  |  |

|                                                                         | 4.1                                                                                          | Design pro   | ocesses                                             | 15 |  |  |

|                                                                         | 4.2                                                                                          | Electronic   | system design                                       | 16 |  |  |

|                                                                         | 4.3                                                                                          | SoC desig    | ın                                                  | 17 |  |  |

|                                                                         | 4.4                                                                                          | Mixed-sigr   | nal verification and analog block design            | 20 |  |  |

|                                                                         | 4.5                                                                                          | Characteri   | ization and IP preparation                          | 21 |  |  |

| Fiau                                                                    | ıre 1 – El                                                                                   | ectronic de  | esian ecosystem                                     | 7  |  |  |

| 2.5       Table of "Mixed-signal verification" and analog block design" |                                                                                              |              |                                                     |    |  |  |

| -                                                                       |                                                                                              |              |                                                     |    |  |  |

| 5                                                                       |                                                                                              |              |                                                     |    |  |  |

| -                                                                       |                                                                                              |              |                                                     |    |  |  |

| Ŭ                                                                       |                                                                                              |              |                                                     |    |  |  |

| Ŭ                                                                       |                                                                                              |              | <b>.</b>                                            |    |  |  |

| -                                                                       |                                                                                              |              |                                                     |    |  |  |

| Figu                                                                    | ıre 8 – "C                                                                                   | haracteriza  | ation and IP preparation" table                     | 13 |  |  |

| Figure 9 – Multiple marks in one design object                          |                                                                                              |              |                                                     |    |  |  |

| Figu                                                                    | Figure 10 – Multiple marks in the same design objects in the different processes $\ldots 14$ |              |                                                     |    |  |  |

| Figure 11 – Chart of design processes15                                 |                                                                                              |              |                                                     |    |  |  |

### INTERNATIONAL ELECTROTECHNICAL COMMISSION

## DOCUMENTATION ON DESIGN AUTOMATION SUBJECTS – THE BIRD'S-EYE VIEW OF DESIGN LANGUAGES (BVDL)

### FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organizations.

- The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. However, a technical committee may propose the publication of a technical report when it has collected data of a different kind from that which is normally published as an International Standard, for example "state of the art".

IEC 62856, which is a technical report, has been prepared by IEC technical committee 91: Electronics assembly technology:

The text of this technical report is based on the following documents:

| Enquiry draft | Report on voting |  |

|---------------|------------------|--|

| 91/1085/DTR   | 91/1101/RVC      |  |

Full information on the voting for the approval of this technical report can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

#### INTRODUCTION

The automation of design and manufacturing technologies in electronic industries has been evolving world-wide for over three decades with remarkable development speed. Electronic design automation (EDA) technology enables the conceptualization, implementation and validation of electronic systems, that is, transforms the ideas and objectives of the system designers into manufacturable and testable representations in a cost-effective way. It is classified into three key categories such as design methodologies, design libraries and design tools. Standardization involves computer-sensible representations throughout the overall design processes which integrate design libraries and design tools to build a design ecosystem.

In the semiconductor industry EDA technologies have been substantially contributing to the unprecedented industry growth for three decades. To emerging new product lines such as microcontroller, microprocessor, ASIC, FPGA, memories, analog and mixed-signal and System on a chip (SoC) they have been continuously providing a wide range of solutions to meet critical requirements on design productivity enhancement and design quality improvement.

The EDA technical committee (EDA-TC) was formed in JEITA in 1990 in order to take initiatives for international EDA standardization in Japan. Since then, it has been contributing design language standardization such as EDIF, VHDL, Verilog HDL, Delay and Power Calculation (DPC), System C, System Verilog and Power Format, which led to forming the new working group at which experts from the industry and academia were invited and to work with IEC TC93, IEEE DASC, Accellera, Open SystemC Initiatives (OSCI) and others. After having been active for over two decades the need was felt for a bird's-eye view of the existing tens of design languages, and to enhance or develop them in order to set the strategy towards international EDA standardization. EDA-TC initiated the project in early 2009 to develop the Bird's-eye View of Design Languages (BVDL) spreadsheet documentation. It developed the first version in March 2010, in order to have an important participation of design technology experts from the semiconductor industry and academia. It finalized the BVDL documentation combined with the spreadsheet as a JEITA technical report in March 2011.

## DOCUMENTATION ON DESIGN AUTOMATION SUBJECTS – THE BIRD'S-EYE VIEW OF DESIGN LANGUAGES (BVDL)

#### 1 Scope

The BVDL originally aims to make full use of planning and decision-making on EDA standardization activities for a technical expert as well as a manager in JEITA. It facilitates the understanding of the various design languages to show their positioning and features. Also it provides easy overviews of each design language for a newcomer to the EDA standards community and/or for a designer as a user of an EDA design ecosystem. Especially for a design language development that aims to directly join design language development and voting for standardization, it provides metrics to check for duplication among similar languages, consistency to develop the design ecosystem and future challenges for design languages.

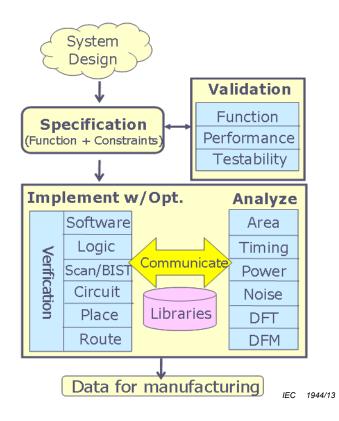

EDA standards provide a mechanism to define common semantics for electronic design ecosystems among various design tools depicted in Figure 1. The state-of-the-art standards are classified into hardware description languages, hardware verification languages, electronic system level design languages, library formats, design constrain formats, interface formats with manufacturing and testing, design data exchange formats, data models and application procedure interfaces (API), etc. Therefore they are generally called standard design languages in a narrow sense. The semiconductor industry has been facing new design complexity barriers and is today facing unprecedented complexities brought by the convergence of product features in terms of silicon process technology, system technology, high gate count and embedded software incorporation. This new design complexity requires integrated EDA solutions and at the same time impacts design ecosystem and standard design languages as well. So a new design language development or new features enhancement to an existing design language is needed. As a result tens of design languages, which might be classified into de jure standard language, de facto standard language, forum standard language and common language used in some community, are developed, enhanced or actually used in the industries, academia and communities world-wide.

Figure 1 – Electronic design ecosystem

This technical report describes features for existing design languages, as well as for enhancing and newly developing design languages belonging to the defined design processes of System on a chip (SoC) which ranges from system level design, SoC design implementation and verification, IP block creation and analog block design down to interface data preparation for manufacturing. These simplified design processes might not become obsolete despite the remarkable speed of the evolution of electronic design automation and seem easier to understand for a non-EDA expert.

Thirty-three design languages have been chosen and each feature of their latest version as of March 2011 is reflected in this report:

UML Esterel Rosetta SystemC SystemC-AMS IBIS CITI TouchStone BSDL System Verilog VHDL Verilog HDL UPF CPF

e language PSL FSDB SDC DEF Open Access SDF GDS II OASIS STIL WGL Verilog-A Verilog-AMS SPICE VHDL-AMS LEF Liberty CDL IP-XACT.